西藏三維光子互連芯片多芯MT-FA光組件集成方案

三維光子互連芯片的一個重要優(yōu)點是其高帶寬密度。傳統(tǒng)的電子I/O接口難以有效地擴展到超過100 Gbps的帶寬密度,而三維光子互連芯片則可以實現(xiàn)Tbps級別的帶寬密度。這種高帶寬密度使得三維光子互連芯片能夠支持更高密度的數(shù)據(jù)交換和處理,滿足未來計算系統(tǒng)對高帶寬的需求。除了高速傳輸和低能耗外,三維光子互連芯片還具備長距離傳輸能力。傳統(tǒng)的電子I/O傳輸距離有限,即使使用中繼器也難以實現(xiàn)長距離傳輸。而三維光子互連芯片則可以通過光纖等介質(zhì)實現(xiàn)數(shù)公里甚至更遠的傳輸距離。這一特性使得三維光子互連芯片在遠程通信、數(shù)據(jù)中心互聯(lián)等領(lǐng)域具有普遍應用前景。利用三維光子互連芯片,可以明顯降低云計算中心的能耗,推動綠色計算的發(fā)展。西藏三維光子互連芯片多芯MT-FA光組件集成方案

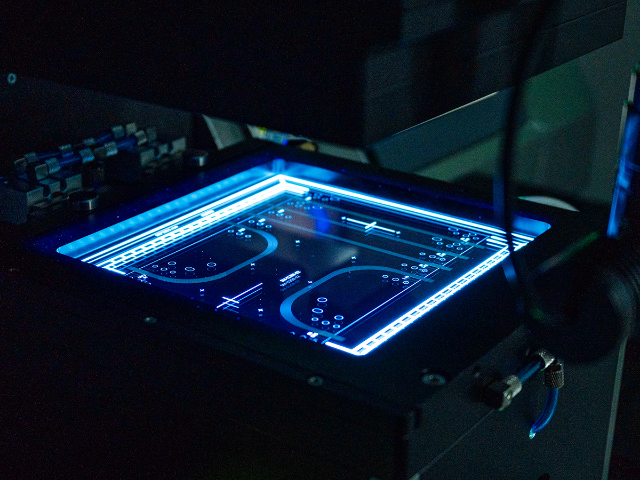

從制造工藝層面看,多芯MT-FA光耦合器的突破源于材料科學與精密工程的深度融合。其重要部件MT插芯采用陶瓷-金屬復合材料,通過超精密磨削將芯間距誤差控制在±0.5μm以內(nèi),配合新型Hybrid353ND系列膠水實現(xiàn)UV固化定位與353ND環(huán)氧樹脂性能的雙重保障,有效解決了傳統(tǒng)工藝中因熱應力導致的通道偏移問題。在三維集成方面,該器件通過銅錫熱壓鍵合技術(shù),在15μm間距上形成2304個微米級互連點,剪切強度達114.9MPa,同時將電容降低至10fF,使光子層與電子層的信號同步誤差小于2ps。這種結(jié)構(gòu)不僅支持多波長復用傳輸,還能通過微盤調(diào)制器與鍺硅光電二極管的集成,實現(xiàn)單比特50fJ的較低能耗。實際應用中,多芯MT-FA已驗證可在4m單模光纖傳輸下保持誤碼率低于4×10?1?,其緊湊型設(shè)計(0.3mm2芯片面積)更適配CPO(共封裝光學)架構(gòu),為數(shù)據(jù)中心從100G向800G/1.6T演進提供了可量產(chǎn)的解決方案。隨著三維光子集成技術(shù)向全光互連架構(gòu)發(fā)展,多芯MT-FA的光耦合效率與集成密度將持續(xù)優(yōu)化,成為突破AI算力瓶頸的關(guān)鍵基礎(chǔ)設(shè)施。西藏三維光子互連芯片多芯MT-FA光組件集成方案三維光子互連芯片的毛細管力對準技術(shù),利用表面張力實現(xiàn)自組裝。

在高頻信號傳輸中,速度是決定性能的關(guān)鍵因素之一。光子互連利用光子在光纖或波導中傳播的特性,實現(xiàn)了接近光速的數(shù)據(jù)傳輸。與電信號在銅纜中傳輸相比,光信號的傳播速度要快得多,從而帶來了極低的傳輸延遲。這種低延遲特性對于實時性要求極高的應用場景尤為重要,如高頻交易、遠程手術(shù)和虛擬現(xiàn)實等。隨著數(shù)據(jù)量的破壞性增長,對傳輸帶寬的需求也在不斷增加。傳統(tǒng)的銅互連技術(shù)受限于電信號的物理特性,其傳輸帶寬難以大幅提升。而光子互連則通過光信號的多波長復用技術(shù),實現(xiàn)了極高的傳輸帶寬。光子信號在光纖中傳播時,可以復用在不同的波長上,從而大幅增加可傳輸?shù)臄?shù)據(jù)量。這使得光子互連能夠輕松滿足未來高頻信號傳輸對帶寬的極高要求。

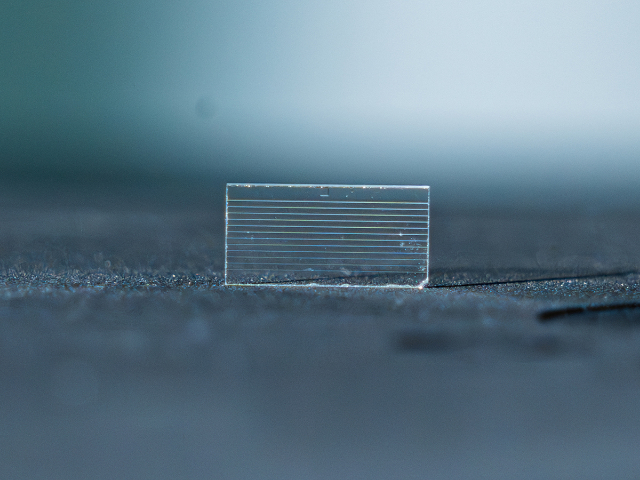

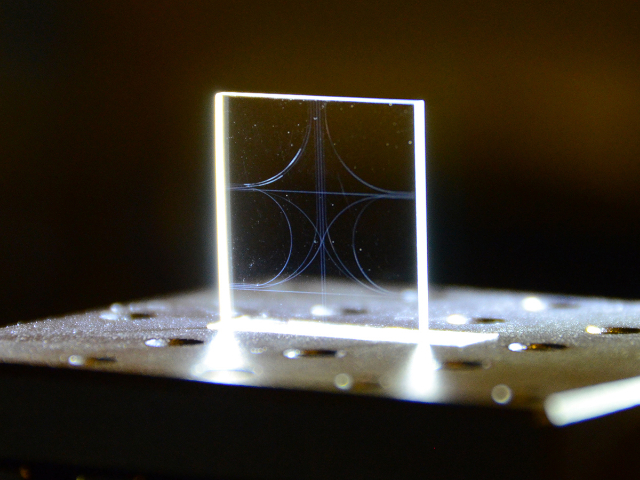

多芯MT-FA光組件的三維芯片互連標準正成為光通信與集成電路交叉領(lǐng)域的關(guān)鍵技術(shù)規(guī)范。其重要在于通過高精度三維互連架構(gòu),實現(xiàn)多通道光信號與電信號的協(xié)同傳輸。在物理結(jié)構(gòu)層面,該標準要求MT-FA組件的端面研磨角度需精確控制在42.5°±0.5°范圍內(nèi),以確保全反射條件下光信號的低損耗耦合。配合低損耗MT插芯與亞微米級V槽定位技術(shù),單通道插損可控制在0.2dB以下,通道間距誤差不超過±0.5μm。這種設(shè)計使得800G光模塊中16通道并行傳輸?shù)拇當_抑制比達到45dB以上,滿足AI算力集群對數(shù)據(jù)傳輸完整性的嚴苛要求。三維互連的垂直維度則依賴硅通孔(TSV)或玻璃通孔(TGV)技術(shù),其中TSV直徑已從10μm向1μm量級突破,深寬比提升至20:1,配合原子層沉積(ALD)工藝形成的共形絕緣層,有效解決了微孔電鍍填充的均勻性問題。實驗數(shù)據(jù)顯示,采用0.9μm間距TSV陣列的芯片堆疊,互連密度較傳統(tǒng)方案提升3個數(shù)量級,通信速度突破10Tbps,能源效率優(yōu)化至20倍,為高密度計算提供了物理層支撐。三維光子互連芯片的倒裝芯片鍵合技術(shù),優(yōu)化高性能計算的熱管理。

從技術(shù)實現(xiàn)層面看,多芯MT-FA光組件的集成需攻克三大重要挑戰(zhàn):其一,高精度制造工藝要求光纖陣列的通道間距誤差控制在±0.5μm以內(nèi),以確保與TSV孔徑的精確對齊;其二,低插損特性需通過特殊研磨工藝實現(xiàn),典型產(chǎn)品插入損耗≤0.35dB,回波損耗≥60dB,滿足AI算力場景下長時間高負載運行的穩(wěn)定性需求;其三,熱應力管理要求組件材料與硅基板的熱膨脹系數(shù)匹配度極高,避免因溫度波動導致的層間剝離。實際應用中,該組件已成功應用于1.6T光模塊的3D封裝,通過將光引擎與電芯片垂直堆疊,使單模塊封裝體積縮小40%,同時支持800G至1.6T速率的無縫升級。在AI服務器背板互聯(lián)場景下,MT-FA組件可實現(xiàn)每平方毫米10萬通道的光互連密度,較傳統(tǒng)方案提升2個數(shù)量級。這種技術(shù)突破不僅推動了三維芯片向更高集成度演進,更為下一代光計算架構(gòu)提供了基礎(chǔ)支撐,預示著光互連技術(shù)將成為突破內(nèi)存墻功耗墻的重要驅(qū)動力。相比電子通信,三維光子互連芯片具有更低的功耗和更高的能效比。濟南多芯MT-FA光組件在三維芯片中的集成

在三維光子互連芯片中,可以利用空間模式復用(SDM)技術(shù)。西藏三維光子互連芯片多芯MT-FA光組件集成方案

在工藝實現(xiàn)層面,三維光子互連芯片的多芯MT-FA封裝需攻克多重技術(shù)挑戰(zhàn)。光纖陣列的制備涉及高精度V槽加工與紫外膠固化工藝,采用新型Hybrid353ND系列膠水可同時實現(xiàn)UV定位與結(jié)構(gòu)粘接,簡化流程并降低應力。芯片堆疊環(huán)節(jié),通過混合鍵合技術(shù)將光子芯片與CMOS驅(qū)動層直接鍵合,鍵合間距突破至10μm以下,較傳統(tǒng)焊料凸點提升5倍集成度。熱管理方面,針對三維堆疊的散熱難題,研發(fā)團隊開發(fā)了微流體冷卻通道與導熱硅中介層復合結(jié)構(gòu),使1.6T光模塊在滿負荷運行時的結(jié)溫控制在85℃以內(nèi),較空氣冷卻方案降溫效率提升40%。此外,為適配CPO(共封裝光學)架構(gòu),MT-FA組件的端面角度和通道間距可定制化調(diào)整,支持從100G到1.6T的全速率覆蓋,其低插損特性(單通道損耗<0.2dB)確保了光信號在超長距離傳輸中的完整性。隨著AI大模型參數(shù)規(guī)模突破萬億級,該技術(shù)有望成為下一代數(shù)據(jù)中心互聯(lián)的重要解決方案,推動光通信向光子集成+電子協(xié)同的異構(gòu)計算范式演進。西藏三維光子互連芯片多芯MT-FA光組件集成方案

- 多芯/空芯光纖連接器現(xiàn)貨 2025-12-24

- 福州多芯光纖連接器產(chǎn)品 2025-12-24

- 南昌多芯光纖連接器 FC/PC APC混合 2025-12-23

- 廣東空芯光纖連接器材料 2025-12-23

- 浙江空芯光纖連接器標準 2025-12-23

- 石家莊多芯光纖連接器SC/PC APC混合 2025-12-23

- 杭州多芯光纖連接器 SC/PC 2025-12-23

- 天津空芯光纖連接器的作用 2025-12-23

- 昆明高能激光空芯光纖 2025-12-23

- 河南多芯光纖連接器價格 2025-12-23

- 南通CH9頻率語音電臺供應商 2025-12-24

- 寧波超融合系統(tǒng)廠商排名 2025-12-24

- 吉林數(shù)據(jù)超融合系統(tǒng)廠商 2025-12-24

- 河北抽屜式低壓柜生產(chǎn)廠家 2025-12-24

- 舟山CH16頻率語音電臺系統(tǒng) 2025-12-24

- 網(wǎng)絡(luò)醫(yī)務系統(tǒng)專賣 2025-12-24

- 錫山區(qū)本地信息系統(tǒng)集成服務商24小時服務 2025-12-24

- 無線定位器追蹤 2025-12-24

- 中山夾耳耳機喇叭價格 2025-12-24

- 昆山耐用毫米波通信質(zhì)量 2025-12-24