-

儀器儀表測試UFS信號完整性測試快速出具檢測報告

儀器儀表測試UFS信號完整性測試快速出具檢測報告UFS 信號完整性之信號上升 / 下降時間優化 優化信號上升 / 下降時間對 UFS 信號完整性意義重大。在 UFS 數據傳輸中,合適的上升 / 下降時間能減少信號間干擾,保障信號質量。若上升 / 下降時間過短,信號的高頻分量增加,會導致傳輸線損耗增大、串擾加劇;若過長,則信號傳輸速度受限,影響系統性能。例如,在設計 UFS 信號時,需根據傳輸線特性、系統頻率等因素,合理調整驅動芯片參數,優化信號的上升 / 下降時間。通過精確控制信號的變化速率,可使信號在保證傳輸速度的同時,降低信號完整性風險,實現高效、可靠的數據傳輸。 UFS 信號完整性測試之發射端測試要點?儀器儀表測試UFS信號...

2025-12-15 -

夾具測試UFS信號完整性測試信號完整性測試

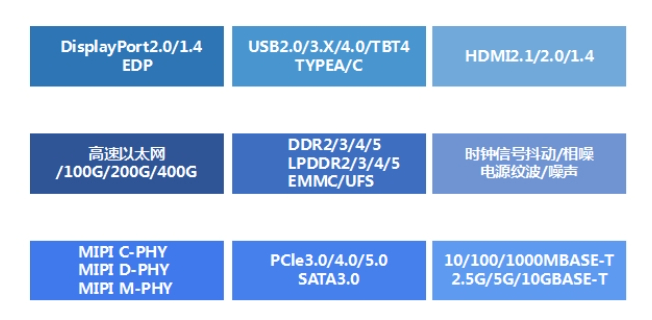

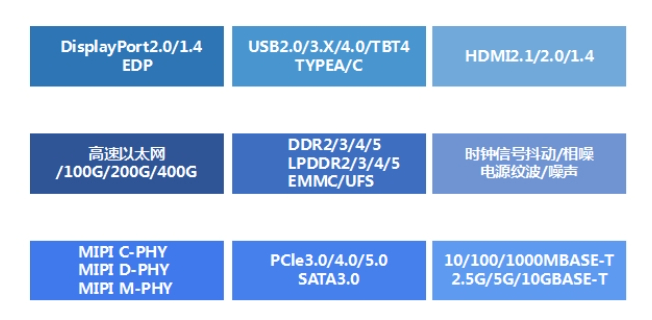

夾具測試UFS信號完整性測試信號完整性測試UFS 信號完整性測試之不同版本 UFS 測試差異 不同版本 UFS 信號完整性測試有差異。UFS 4.0 比 UFS 3.1 傳輸速率更高,測試時對儀器帶寬、采樣率要求更嚴。UFS 4.0 需測試 23.2Gbps 速率下的信號,而 UFS 3.1 比較高 11.6Gbps 。高版本 UFS 對眼圖參數、抖動控制更苛刻。測試時需根據具體版本調整測試標準與儀器設置,確保測試符合對應版本的技術規范。 UFS 信號完整性測試之供應鏈測試協作 UFS 供應鏈中,各環節測試協作很重要。芯片廠商、板卡制造商、整機廠商需統一測試標準。芯片廠商提供芯片信號參數,板卡廠商...

2025-12-15 -

高速信號UFS信號完整性測試端口測試

高速信號UFS信號完整性測試端口測試UFS 信號完整性測試之量子加密關聯 隨著量子加密技術發展,UFS 信號完整性測試與之產生關聯。量子加密的安全性依賴于量子態的穩定性,而 UFS 信號傳輸質量會影響量子加密數據的存儲與讀取。若 UFS 信號完整性差,量子加密數據在存儲過程中可能發生錯誤,導致失敗。測試時,需在量子加密環境下評估 UFS 信號。一方面優化 UFS 信號傳輸,確保數據準確存儲;另一方面,研究量子加密對 UFS 信號的特殊要求,如對信號噪聲容限的更高標準。保障二者協同工作,既提升數據安全性,又保證 UFS 存儲性能。 UFS 信號完整性測試之長期穩定性測試?高速信號UFS信號完整性測試端口測試 UFS 信...

2025-12-15 -

信息化UFS信號完整性測試回波損耗測試

信息化UFS信號完整性測試回波損耗測試UFS 信號完整性測試之接口設計要點 UFS 接口設計關乎信號完整性。接口處要保證良好的電氣連接,防止接觸不良導致信號中斷或失真。接口的阻抗要與傳輸線匹配,減少信號反射。在測試中,檢查接口的針腳布局是否合理,是否符合標準。例如,標準規定針腳布局要保證高速信號傳輸時信號質量穩定。優化接口設計,能為 UFS 信號完整性提供可靠連接,確保數據順暢傳輸。 UFS 信號完整性測試之電源穩定性影響 電源穩定性對 UFS 信號完整性至關重要。電源紋波過大,會引入噪聲,干擾信號傳輸。例如,要求電源紋波<50mVpp ,需配備大容量電容(10μF+0.1μF)濾波。若電源不...

2025-12-15 -

信息化UFS信號完整性測試兼容性測試

信息化UFS信號完整性測試兼容性測試UFS 信號完整性測試之量子加密關聯 隨著量子加密技術發展,UFS 信號完整性測試與之產生關聯。量子加密的安全性依賴于量子態的穩定性,而 UFS 信號傳輸質量會影響量子加密數據的存儲與讀取。若 UFS 信號完整性差,量子加密數據在存儲過程中可能發生錯誤,導致失敗。測試時,需在量子加密環境下評估 UFS 信號。一方面優化 UFS 信號傳輸,確保數據準確存儲;另一方面,研究量子加密對 UFS 信號的特殊要求,如對信號噪聲容限的更高標準。保障二者協同工作,既提升數據安全性,又保證 UFS 存儲性能。 UFS 信號完整性測試之物理層協議影響?信息化UFS信號完整性測試兼容性測試 UFS 信...

-

si信號完整性UFS信號完整性測試檢測

si信號完整性UFS信號完整性測試檢測UFS 信號完整性與傳輸線損耗 傳輸線損耗是影響 UFS 信號完整性的重要因素。在 UFS 數據傳輸過程中,信號沿傳輸線傳播時,會因導體電阻、介質損耗等原因逐漸衰減。高頻信號尤為明顯,其在傳輸線中傳播,能量不斷被消耗,導致信號幅度降低、波形變形。例如,較長的 PCB 走線、低質量的連接器,都會加劇傳輸線損耗。為降低損耗對信號完整性的影響,一方面要選用低損耗的 PCB 板材,精心設計傳輸線參數,像控制合適的走線長度、線寬等;另一方面,可借助信號調理電路,對衰減的信號進行放大、整形。有效管控傳輸線損耗,是維持 UFS 信號完整性、保障高速數據可靠傳輸的關鍵舉措。 UFS 信號完整性測試之...

2025-12-15 -

多端口矩陣測試UFS信號完整性測試RX

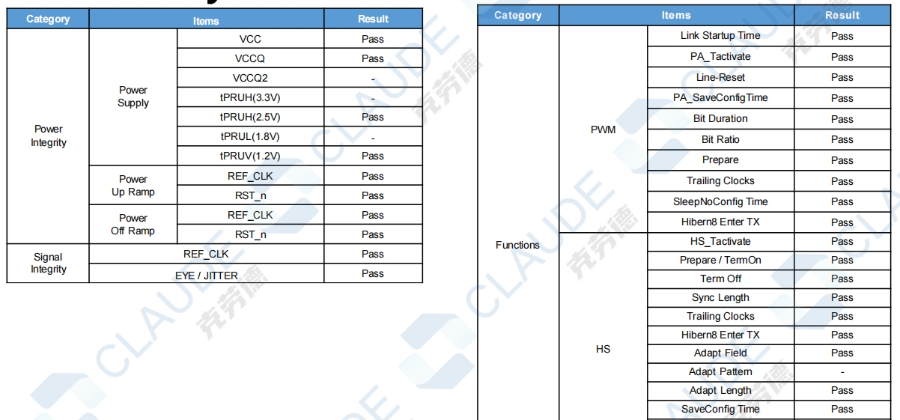

多端口矩陣測試UFS信號完整性測試RXUFS 信號完整性之電源完整性關聯 電源完整性與 UFS 信號完整性緊密相連。UFS 設備穩定工作依賴良好的電源供應。電源紋波過大,會在芯片內部產生噪聲,干擾信號傳輸,影響信號的電壓穩定性,導致信號電平波動,增加誤碼率。同時,電源分配網絡(PDN)的阻抗特性也至關重要。在高頻段,若 PDN 阻抗過高,會使電源電壓出現較大壓降,影響芯片正常工作,進而破壞信號完整性。例如,在設計 UFS 電源時,需使用大容量電容(如 10μF + 0.1μF)來降低電源紋波,構建低阻抗的 PDN,確保電源穩定,為 UFS 信號完整性創造良好的電源環境。 UFS 信號完整性測試之供應鏈測試協作?多端口矩陣...

2025-12-15 -

電氣性能測試UFS信號完整性測試信號眼圖

電氣性能測試UFS信號完整性測試信號眼圖UFS 信號完整性測試之信號完整性與行業標準遵循 UFS 信號完整性測試需遵循行業標準。MIPI 聯盟和 JEDEC 協會制定相關規范,如眼圖參數、抖動要求等。遵循標準測試,能確保 UFS 設備兼容性與互操作性。在測試過程中,嚴格按照標準操作,比對參數。只有符合行業標準,UFS 設備才能在市場上流通,推動行業健康發展,保障產業鏈各環節協同工作。 UFS 信號完整性測試之信號完整性與新技術應用 隨著新技術發展,UFS 信號完整性面臨新挑戰與機遇。如 5G、人工智能推動 UFS 傳輸速率提升,對信號完整性要求更高。同時,新的信號處理技術、材料應用,可改善信號完...

2025-12-15 -

UFS信號完整性測試操作

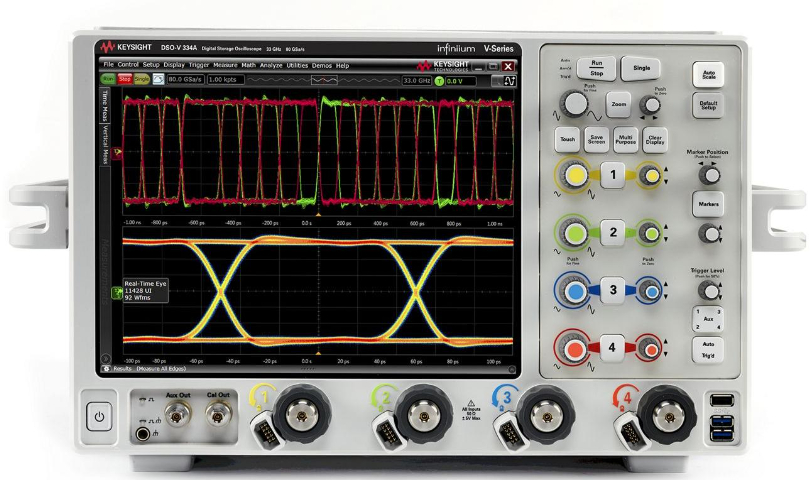

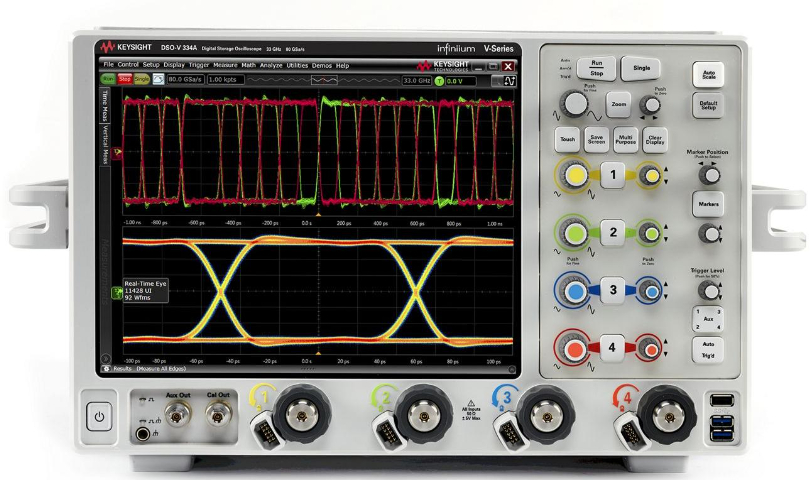

UFS信號完整性測試操作1.測試基礎要求UFS信號測試需在23±3℃環境進行,要求示波器帶寬≥16GHz(UFS3.1需33GHz),采樣率≥80GS/s。測試點應選在UFS芯片ballout1mm范圍內,使用40GHz差分探頭,阻抗匹配100Ω±5%。需同時監測VCCQ(1.2V)和VCC(3.3V)電源噪聲。2.眼圖標準解讀JEDEC標準規定:HS-Gear3眼高≥80mV,眼寬≥0.7UI;HS-Gear4要求提升15%。實測需累積1E6比特數據,重點關注垂直閉合(噪聲導致)和水平閉合(抖動導致)。合格樣本眼圖應呈現清晰鉆石型。3.抖動分解方法使用相位噪聲分析軟件將總抖動(Tj)分解:隨機抖動(Rj)應<1.5...

-

轉接板UFS信號完整性測試插入損耗測試

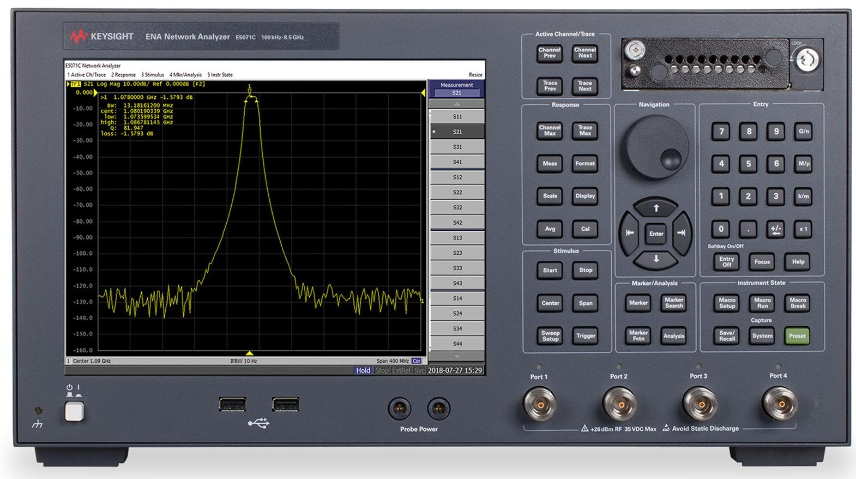

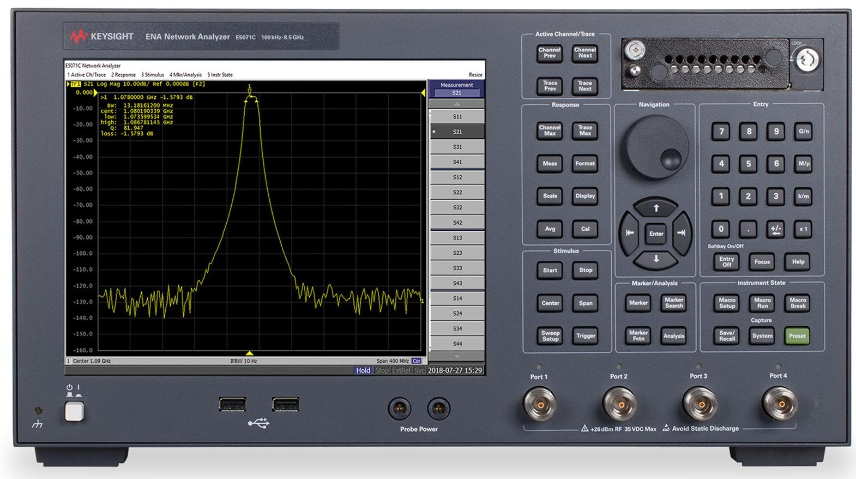

轉接板UFS信號完整性測試插入損耗測試UFS 信號完整性測試之接收端測試要點 接收端測試在 UFS 信號完整性測試中同樣關鍵。要評估 UFS 控制器接收端靈敏度與信號完整性。靈敏度決定接收端能否準確接收微弱信號。信號完整性差,如存在噪聲、失真,接收端易誤判數據。測試時用校準的抖動源產生壓力信號,測試設備經 CDR 恢復時鐘信號,再測誤碼率。若誤碼率高,需優化接收端電路設計,提高接收端對信號的處理能力,保障 UFS 接收信號的完整性。 UFS 信號完整性測試工具介紹 在 UFS 信號完整性測試中,專業工具不可或缺。如 Keysight 的 U7249E 一致性測試軟件,能精確測試信號參數,判斷是...

-

高速信號UFS信號完整性測試項目

高速信號UFS信號完整性測試項目UFS 信號完整性之數據速率關聯 數據速率與 UFS 信號完整性緊密相關。隨著 UFS 技術發展,數據傳輸速率不斷提升,對信號完整性要求愈發嚴苛。在高速率下,信號傳輸過程中的損耗、反射、串擾等問題更加突出。例如,UFS 4.0 相比 UFS 3.1 數據速率大幅提高,信號在傳輸線中傳播時,高頻分量更容易衰減,微小的信號完整性問題都可能導致大量數據傳輸錯誤。為適應高數據速率,需在硬件設計上采用更先進的工藝、材料,優化傳輸線結構,提升信號抗干擾能力;在測試環節,也需針對高速信號特點,制定更嚴格的測試標準和方法,保障 UFS 在高數據速率下維持良好信號完整性。 UFS 信號完整性之阻抗匹配...

2025-12-14 -

信號分析UFS信號完整性測試測試流程

信號分析UFS信號完整性測試測試流程UFS 信號完整性與傳輸線損耗 傳輸線損耗是影響 UFS 信號完整性的重要因素。在 UFS 數據傳輸過程中,信號沿傳輸線傳播時,會因導體電阻、介質損耗等原因逐漸衰減。高頻信號尤為明顯,其在傳輸線中傳播,能量不斷被消耗,導致信號幅度降低、波形變形。例如,較長的 PCB 走線、低質量的連接器,都會加劇傳輸線損耗。為降低損耗對信號完整性的影響,一方面要選用低損耗的 PCB 板材,精心設計傳輸線參數,像控制合適的走線長度、線寬等;另一方面,可借助信號調理電路,對衰減的信號進行放大、整形。有效管控傳輸線損耗,是維持 UFS 信號完整性、保障高速數據可靠傳輸的關鍵舉措。 UFS 信號完整性測試之...

-

軟件測試UFS信號完整性測試方案商

軟件測試UFS信號完整性測試方案商UFS信號完整性測試的重要性UFS(通用閃存存儲)作為高速存儲接口,其信號完整性直接影響數據傳輸的穩定性和可靠性。隨著UFS3.1/4.0速率提升至23.2Gbps,微小的信號失真即可導致嚴重的誤碼問題。信號完整性測試能確保關鍵參數(如眼圖、抖動、阻抗匹配)符合JEDEC和MIPI標準,避免因信號劣化引發系統故障或數據錯誤。在研發階段,SI測試可快速定位設計缺陷(如走線過長、阻抗失配),優化PCB布局,降低后期改版風險。量產階段則通過統計測試確保生產一致性,提升產品良率。此外,嚴苛環境測試(如高溫、振動)能驗證產品的長期可靠性。隨著5G、AI等應用對存儲性能要求不斷提高,完善的UFS信號完...

2025-12-14 -

解決方案UFS信號完整性測試物理層測試

解決方案UFS信號完整性測試物理層測試UFS 信號完整性測試之測試流程概述 UFS 信號完整性測試有嚴謹流程。首先搭建測試環境,連接好 UFS 設備、測試儀器等。接著對發射端進行測試,測量信號電壓、時間等參數。然后測試接收端,評估靈敏度與誤碼率。過程中,利用 TDR 測阻抗,用示波器觀察眼圖、抖動等。測試完成后,分析數據,判斷信號完整性是否達標。若不達標,排查問題并整改,重新測試,確保 UFS 信號滿足性能要求。 UFS 信號完整性測試之環境因素考量 測試 UFS 信號完整性時,環境因素不可忽視。溫度變化可能影響電子元件性能,導致信號參數改變。濕度太高,線路可能受潮,引發短路等問題,影響信號傳輸。電磁環境復雜...

2025-12-14 -

解決方案UFS信號完整性測試(SI/PI)

解決方案UFS信號完整性測試(SI/PI)UFS 信號完整性測試之接收端測試要點 接收端測試在 UFS 信號完整性測試中同樣關鍵。要評估 UFS 控制器接收端靈敏度與信號完整性。靈敏度決定接收端能否準確接收微弱信號。信號完整性差,如存在噪聲、失真,接收端易誤判數據。測試時用校準的抖動源產生壓力信號,測試設備經 CDR 恢復時鐘信號,再測誤碼率。若誤碼率高,需優化接收端電路設計,提高接收端對信號的處理能力,保障 UFS 接收信號的完整性。 UFS 信號完整性測試工具介紹 在 UFS 信號完整性測試中,專業工具不可或缺。如 Keysight 的 U7249E 一致性測試軟件,能精確測試信號參數,判斷是...

2025-12-14 -

數字信號UFS信號完整性測試一致性測試

數字信號UFS信號完整性測試一致性測試UFS 信號完整性重心要義 UFS 信號完整性,是確保 UFS 存儲設備內信號在傳輸路徑上保持完整的關鍵特性。在 UFS 系統里,數據借由各類信號進行存儲與傳輸,信號的完整性直接左右數據的準確性和系統穩定性。從本質上講,它聚焦于信號在傳輸過程中,能否維持原本的電壓、頻率、相位等關鍵參數。一旦信號完整性欠佳,數據傳輸便可能出錯,像數據丟失、誤碼等狀況就會接踵而至。比如在高速讀寫時,不穩定的信號或許會致使讀取到錯誤數據,寫入的數據也無法正確存儲。因此,保障 UFS 信號完整性,是實現 UFS 設備高效、可靠運行的基石,對提升存儲性能、確保數據安全起著決定性作用。 UFS 信號完整性測試之...

2025-12-14 -

物理層數字信號UFS信號完整性測試M-PHY測試

物理層數字信號UFS信號完整性測試M-PHY測試UFS 信號完整性與時鐘信號關系 時鐘信號在 UFS 信號完整性中扮演關鍵角色。UFS 設備依靠時鐘信號來同步數據的發送與接收,確保數據在正確時刻被采樣、處理。穩定、精細的時鐘信號是保障信號完整性的基礎。若時鐘信號出現頻率偏差、抖動等問題,會使數據傳輸的時序錯亂。比如時鐘頻率漂移,會導致發送端和接收端數據速率不一致,接收端無法在正確時刻采樣數據,引發誤碼;時鐘抖動則會增大數據傳輸的不確定性。因此,在 UFS 系統設計中,要精心設計時鐘電路,采用高精度時鐘源,做好時鐘信號的隔離、濾波,保證時鐘信號穩定,為 UFS 信號完整性提供堅實支撐。 UFS 信號完整性測試之信號完整性與通信穩定性...

2025-12-14 -

數字信號UFS信號完整性測試物理層測試

數字信號UFS信號完整性測試物理層測試UFS 信號完整性之信號上升 / 下降時間優化 優化信號上升 / 下降時間對 UFS 信號完整性意義重大。在 UFS 數據傳輸中,合適的上升 / 下降時間能減少信號間干擾,保障信號質量。若上升 / 下降時間過短,信號的高頻分量增加,會導致傳輸線損耗增大、串擾加劇;若過長,則信號傳輸速度受限,影響系統性能。例如,在設計 UFS 信號時,需根據傳輸線特性、系統頻率等因素,合理調整驅動芯片參數,優化信號的上升 / 下降時間。通過精確控制信號的變化速率,可使信號在保證傳輸速度的同時,降低信號完整性風險,實現高效、可靠的數據傳輸。 UFS 信號完整性測試之信號完整性與產品質量?數字信號UFS信...

-

儀器儀表測試UFS信號完整性測試方案商

儀器儀表測試UFS信號完整性測試方案商UFS 信號完整性測試之信號完整性與行業標準遵循 UFS 信號完整性測試需遵循行業標準。MIPI 聯盟和 JEDEC 協會制定相關規范,如眼圖參數、抖動要求等。遵循標準測試,能確保 UFS 設備兼容性與互操作性。在測試過程中,嚴格按照標準操作,比對參數。只有符合行業標準,UFS 設備才能在市場上流通,推動行業健康發展,保障產業鏈各環節協同工作。 UFS 信號完整性測試之信號完整性與新技術應用 隨著新技術發展,UFS 信號完整性面臨新挑戰與機遇。如 5G、人工智能推動 UFS 傳輸速率提升,對信號完整性要求更高。同時,新的信號處理技術、材料應用,可改善信號完...

2025-12-14 -

夾具測試UFS信號完整性測試檢測

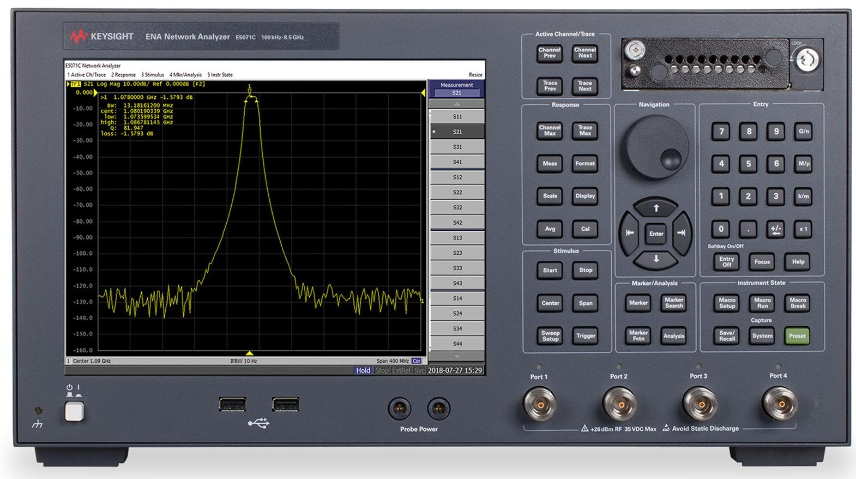

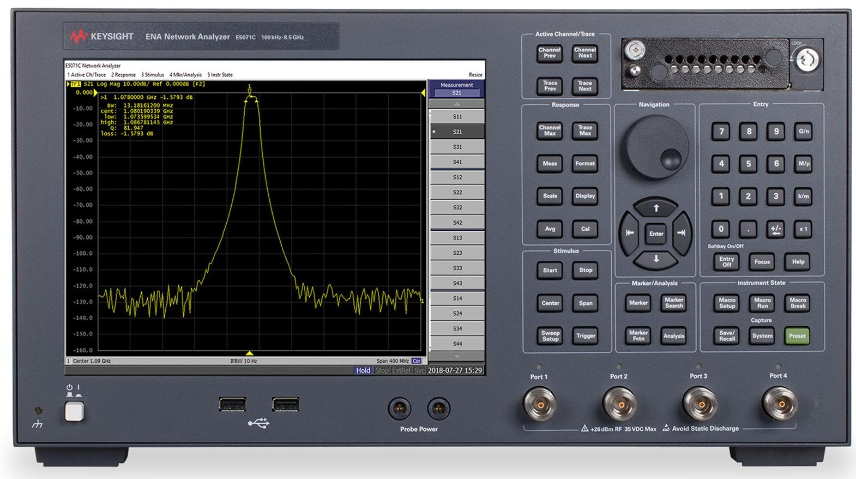

夾具測試UFS信號完整性測試檢測UFS 信號完整性之測試方法基礎 UFS 信號完整性測試是確保其性能的關鍵環節。常用測試方法包括使用示波器進行眼圖測試,通過觀察眼圖的眼高、眼寬等參數,評估信號質量和噪聲容限。抖動測試則借助專業儀器,測量信號的隨機抖動(RJ)和周期抖動(PJ),確定總抖動(TJ)是否符合標準。此外,還可通過網絡分析儀測試傳輸線的 S 參數,分析信號傳輸過程中的反射、損耗等情況。在測試時,要嚴格按照 UFS 標準設置測試條件,如不同速率下的信號參數要求。通過***、準確的測試,能及時發現 UFS 信號完整性問題,為優化設計提供依據。 UFS 信號完整性測試之不同應用場景測試差異?夾具測試UFS信號完整...

2025-12-14 -

轉接板UFS信號完整性測試方案商

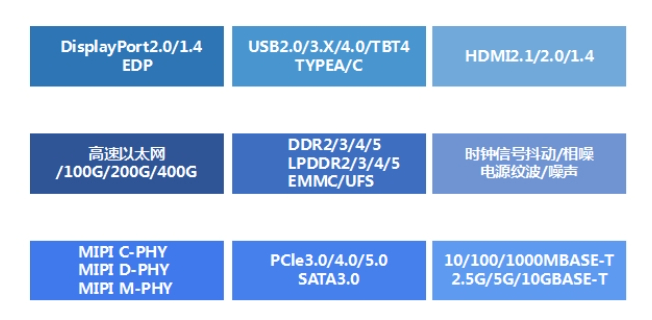

轉接板UFS信號完整性測試方案商UFS信號完整性基礎概念UFS信號完整性測試是驗證高速串行接口性能的關鍵環節,主要評估信號在傳輸過程中的質量衰減。測試頻率覆蓋1.5GHz至11.6GHz(UFS3.1標準),重點關注差分信號的幅度、時序和噪聲特性。典型測試參數包括眼圖高度/寬度、抖動、插入損耗等,需滿足JEDECJESD220C規范要求。MIPIM-PHY物理層測試UFS采用MIPIM-PHY作為物理層接口,測試需關注HS-Gear3/4模式下的信號特性。關鍵指標:差分幅度200-400mVpp,共模電壓0.9-1.2V,上升時間<35ps。測試需使用16GHz以上帶寬示波器,通過TDR驗證阻抗匹配(100Ω±10%)。Un...

2025-12-14 -

物理層信號完整性測試(SI/PI)UFS信號完整性測試系列

物理層信號完整性測試(SI/PI)UFS信號完整性測試系列UFS 信號完整性測試之共模干擾抑制 UFS 采用差分信號技術抑制共模干擾,保障信號完整性。差分信號由兩個幅度相等、相位相反信號組成。共模干擾同時影響這兩個信號,接收端通過比較二者差值,消除共模干擾影響。在測試中,要檢查差分信號傳輸路徑是否合理,防止外界干擾破壞差分信號特性。抑制共模干擾,能提升 UFS 信號抗干擾能力,讓信號在復雜電磁環境下,仍保持完整性,穩定傳輸數據。 UFS 信號完整性測試之信號失真排查 信號失真會嚴重影響 UFS 信號完整性。電磁干擾、反射、串擾等都能導致信號失真。測試時,通過觀察信號波形、分析頻譜等方法排查失真原因。若因電磁干擾,...

2025-12-14 -

信息化UFS信號完整性測試操作

信息化UFS信號完整性測試操作UFS 硬件架構與信號完整性關聯 UFS 硬件架構設計影響信號完整性。差分對下方要保留連續地平面,防止跨分割,避免信號反射。接收端添加 100Ω 差分端接電阻(集成于主控或外置),能匹配阻抗,減少信號失真。相鄰信號對間距≥3 倍線寬,并用地屏蔽過孔(Guard Via),可抑制串擾。合理規劃硬件架構,為信號完整性提供物理基礎,確保 UFS 數據高速、準確傳輸,讓設備發揮比較好性能。 UFS 信號完整性測試之信號質量優 化優化 UFS 信號質量是信號完整性測試的目的之一。優化信號上升 / 下降時間,能讓信號更清晰,減少碼間干擾。借助信號完整性分析工具,如 A...

2025-12-13 -

軟件測試UFS信號完整性測試保證質量

軟件測試UFS信號完整性測試保證質量UFS 信號完整性測試之信號完整性與用戶體驗 UFS 信號完整性直接影響用戶體驗。信號穩定,設備讀寫速度快、運行流暢。當信號出現問題,手機等設備可能卡頓、文件傳輸失敗。在測試 UFS 信號完整性時,從用戶角度出發,模擬實際使用場景。保障信號完整性,提升設備性能,為用戶帶來便捷、高效使用體驗,提高用戶滿意度。 UFS 信號完整性測試之常見誤區 UFS 信號完整性測試易陷入一些誤區。比如,*關注眼圖參數達標,忽視實際使用場景下的信號表現。有些測試在理想環境完成,未模擬設備振動、溫度驟變等情況,導致測試結果與實際脫節。還有人認為高成本測試設備就一定能保證測試精細...

2025-12-13 -

數字接口測試系列UFS信號完整性測試示波器和探頭治具

數字接口測試系列UFS信號完整性測試示波器和探頭治具1.測試基礎要求UFS信號測試需在23±3℃環境進行,要求示波器帶寬≥16GHz(UFS3.1需33GHz),采樣率≥80GS/s。測試點應選在UFS芯片ballout1mm范圍內,使用40GHz差分探頭,阻抗匹配100Ω±5%。需同時監測VCCQ(1.2V)和VCC(3.3V)電源噪聲。2.眼圖標準解讀JEDEC標準規定:HS-Gear3眼高≥80mV,眼寬≥0.7UI;HS-Gear4要求提升15%。實測需累積1E6比特數據,重點關注垂直閉合(噪聲導致)和水平閉合(抖動導致)。合格樣本眼圖應呈現清晰鉆石型。3.抖動分解方法使用相位噪聲分析軟件將總抖動(Tj)分解:隨機抖動(Rj)應<1.5...

2025-12-13 -

si信號完整性UFS信號完整性測試時鐘抖動測試

si信號完整性UFS信號完整性測試時鐘抖動測試UFS 信號完整性之抖動影響 抖動對 UFS 信號完整性影響明顯。抖動指信號的定時位置在理想位置附近隨機或周期性變化。在 UFS 數據傳輸中,抖動會使信號的上升沿和下降沿發生偏移,造成采樣時刻不確定性增加。隨機抖動(RJ)具有不可預測性,由熱噪聲、散粒噪聲等引起;周期抖動(PJ)則呈現周期性,多源于時鐘信號干擾、電源噪聲等。當總抖動(TJ)過大,超過一定閾值,接收端就可能誤判信號電平,導致數據傳輸錯誤。例如在 UFS 3.1 @11.6Gbps 速率下,要求 TJ<0.3UI ,RJ<0.1UI 。嚴格控制抖動,是保障 UFS 信號完整性、實現高速、準確數據傳輸的關鍵任務。 UFS ...

-

電氣性能測試UFS信號完整性測試一致性測試

電氣性能測試UFS信號完整性測試一致性測試UFS 信號完整性與數據準確性 UFS 信號完整性直接關系到數據準確性。信號在傳輸中若發生反射、串擾、失真等問題,數據就可能出錯。當信號完整性良好,數據能準確無誤地從發射端傳至接收端。比如在存儲設備讀取數據時,穩定的信號確保讀取數據與原始存儲數據一致。所以,保證 UFS 信號完整性,是實現數據準確傳輸與存儲的重心,對設備數據處理可靠性意義重大。 UFS 信號完整性測試之阻抗控制 阻抗控制是 UFS 信號完整性測試重點。傳輸線阻抗需匹配,否則信號反射嚴重,降低信號質量。通過 TDR(時域反射計)測量傳輸線阻抗,要求為 50Ω±5% 。若阻抗突變,會導致信號畸...

2025-12-13 -

夾具測試UFS信號完整性測試測試流程

夾具測試UFS信號完整性測試測試流程UFS 信號完整性重心要義 UFS 信號完整性,是確保 UFS 存儲設備內信號在傳輸路徑上保持完整的關鍵特性。在 UFS 系統里,數據借由各類信號進行存儲與傳輸,信號的完整性直接左右數據的準確性和系統穩定性。從本質上講,它聚焦于信號在傳輸過程中,能否維持原本的電壓、頻率、相位等關鍵參數。一旦信號完整性欠佳,數據傳輸便可能出錯,像數據丟失、誤碼等狀況就會接踵而至。比如在高速讀寫時,不穩定的信號或許會致使讀取到錯誤數據,寫入的數據也無法正確存儲。因此,保障 UFS 信號完整性,是實現 UFS 設備高效、可靠運行的基石,對提升存儲性能、確保數據安全起著決定性作用。 UFS 信號完整性之眼圖...

-

物理層信號完整性測試(SI/PI)UFS信號完整性測試多端口矩陣測試

物理層信號完整性測試(SI/PI)UFS信號完整性測試多端口矩陣測試UFS 信號完整性之阻抗匹配關鍵 阻抗匹配在 UFS 信號完整性里占據重心地位。傳輸線的阻抗若與 UFS 設備、連接線纜等不匹配,信號傳輸時就會出現反射現象。這就如同聲音在空蕩蕩的大房間里產生回聲,反射的信號會干擾原始信號,致使信號失真、衰減,嚴重影響數據傳輸質量。以 UFS 的差分信號對為例,理想狀態下,需將其阻抗精細控制在 100Ω 。實際設計時,要綜合考量 PCB 板材特性、走線寬度、線間距等因素,利用專業工具進行仿真,優化布線策略,盡可能讓傳輸線阻抗與目標值契合。只有實現良好的阻抗匹配,才能減少信號反射,保障 UFS 信號穩定傳輸,為數據準確讀寫筑牢根基 UFS 信號完整性測...

2025-12-13 -

高速信號UFS信號完整性測試M-PHY測試

高速信號UFS信號完整性測試M-PHY測試UFS 信號完整性之信號上升 / 下降時間優化 優化信號上升 / 下降時間對 UFS 信號完整性意義重大。在 UFS 數據傳輸中,合適的上升 / 下降時間能減少信號間干擾,保障信號質量。若上升 / 下降時間過短,信號的高頻分量增加,會導致傳輸線損耗增大、串擾加劇;若過長,則信號傳輸速度受限,影響系統性能。例如,在設計 UFS 信號時,需根據傳輸線特性、系統頻率等因素,合理調整驅動芯片參數,優化信號的上升 / 下降時間。通過精確控制信號的變化速率,可使信號在保證傳輸速度的同時,降低信號完整性風險,實現高效、可靠的數據傳輸。 UFS 信號完整性測試之高頻信號處理?高速信號UFS信號完整性...

2025-12-13